# Modeling and Validating Distributed Embedded Real-Time Control Systems

Marcel Verhoef

Copyright © 2008, Marcel Verhoef, Dordrecht, The Netherlands

ISBN 978-90-9023705-3

Typeset with LATeX  $2_{\varepsilon}$ Printed by Print Partners Ipskamp, Enschede Cover design by Silvian de Jager

### **Abstract**

The development of complex embedded control systems can be improved significantly by applying formal techniques from control engineering and software engineering. It is shown how these approaches can be combined to improve the design and analysis of high-tech systems, both in theory and practice. The semantics of the integration of two established rigorous techniques has been defined formally in this work. The strength of this integrated semantics is demonstrated by means of a significant industrial case study: the embedded control of a printer paper path, whereby the full development life-cycle from model to realization is covered. The resulting model-driven design approach fits the current engineering practice in industry and is both flexible and effective.

### IPA dissertation series 2009-01

The work in this thesis has been carried out under the auspices of the research school IPA (Institute for Programming research and Algorithmics) and under responsibility of the Embedded Systems Institute as part of the Boderc project, which was partially supported by the Dutch Ministry of Economic Affairs under the Senter TS progam.

# Modeling and Validating Distributed Embedded Real-Time Control Systems

Een wetenschappelijke proeve op het gebied van de Natuurwetenschappen, Wiskunde en Informatica

## Proefschrift

ter verkrijging van de graad van doctor

aan de Radboud Universiteit Nijmegen

op gezag van de rector magnificus, prof. mr. S. C. J. J. Kortmann,

volgens besluit van het College van Decanen

in het openbaar te verdedigen op woensdag 21 januari 2009

om 15.30 uur precies

door

## Marcel Henri Gerard Verhoef

geboren op 5 augustus 1968 te Papendrecht

### Promotor:

Prof. dr. F. W. Vaandrager

# Copromotor:

Dr. J. J. M. Hooman, Radboud Universiteit Nijmegen & Embedded Systems Institute

# Manuscriptcommissie:

Prof. dr. B. P. F. Jacobs

Prof. dr. L. Thiele, Swiss Federal Institute of Technology Zürich (CH)

Prof. dr. ir. P. G. Larsen, Engineering College Aarhus (DK)

Dr. ir. J. P. M. Voeten, Technische Universiteit Eindhoven & Embedded Systems Institute

Dr. ir. J. F. Broenink, Universiteit Twente

# **Preface**

This dissertation is long overdue. Already in 1993, when I graduated from Delft University of Technology, I had been looking for opportunities for a suitable PhD position in Computer Science. But I did not succeed in finding one for various reasons. So, I ended up in industry and spent ten years of my life building complex computer systems and being reasonable successful at it as well. Every now and then there was still this itch that needed satisfaction, of leaving behind unfinished business in academia. But the pressure of working in industry usually kept me far from doing something sensible about it. Having seen several colleagues trying to complete a PhD along side a full time job did not really help either.

All this changed in November 2002 when an advertisement appeared in "Technisch Weekblad" seeking PhD candidates for an applied research project on multi-disciplinary design of real-time embedded control systems at the Embedded Systems Institute. Having struggled with these issues for several years in industry made me decide to seek a position in this project, called BODERC, and the result is now in front of you. It was both a blessing and a challenge returning to academia after so many years. Of course I brought a lot of practical experience to the project, but my academic skills needed polishing, and a lot of it as well. But with the help of old and new friends, I believe we did some interesting work and had a lot of fun doing it.

Of course, papers where produced and conferences were visited. But, perhaps because I was the only BODERC PhD candidate with a priori grey hair, I also got involved in quite a number of interesting "extra-curricular" activities, such as writing a book on VDM++ and organizing a special session at ISOLA'04 which led to the publication of a special issue of the STTT journal which I also co-edited. I have been part of two programme committees of high profile symposia and I visited ETH Zürich, University of Newcastle and the Engineering College at Aarhus several times for joint research work. I was co-organizer of the Industry Day at FM'05 at Newcastle and last but not least I was asked to give two invited lectures at Boston Scientific at Minneapolis, USA, and CSK Systems at Tokyo and Nagoya in Japan on early results of my research work.

So, obviously, completing this thesis before the BODERC project was finished in March 2007 was out of the question. Since my return to Chess, I have been working on this document as any other project in industry: running from one infeasible deadline to another, using floating priority scheduling. But here it is, my magnus opus, and I hope that you enjoy reading it as much as I have enjoyed writing it. Finally, my sincere apologies to those who have tried to provoke and stimulate me to take (and complete) a PhD over the past years and had to wait 15 years on this result!

Voor mijn ouders:

Gerrit Hendrik Verhoef en

Dikkie Adriana van Herk

# **Contents**

| 1 | Intr                                                            | oduction                                                  | 9  |  |  |  |  |  |

|---|-----------------------------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1                                                             | The embedded systems design challenge                     | 12 |  |  |  |  |  |

|   | 1.2                                                             | The BODERC research project                               | 13 |  |  |  |  |  |

|   | 1.3                                                             | The goal of this thesis                                   | 14 |  |  |  |  |  |

|   | 1.4                                                             | Organization of this thesis                               | 15 |  |  |  |  |  |

| 2 | Eva                                                             | luating Embedded System Architectures                     | 19 |  |  |  |  |  |

|   | 2.1                                                             | Introduction                                              | 19 |  |  |  |  |  |

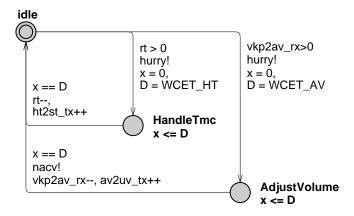

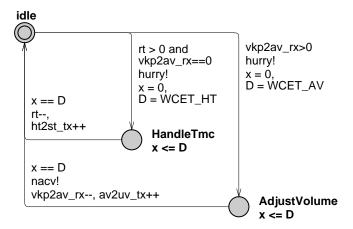

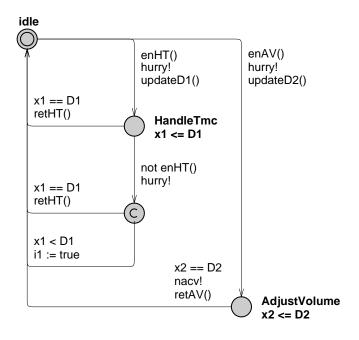

|   | 2.2                                                             | The In-Car Radio Navigation system case study             | 22 |  |  |  |  |  |

|   |                                                                 | 2.2.1 Modeling the system                                 | 22 |  |  |  |  |  |

|   |                                                                 | 2.2.2 Modeling the environment                            | 25 |  |  |  |  |  |

|   |                                                                 | 2.2.3 The modeling and analysis challenge                 | 27 |  |  |  |  |  |

|   | 2.3                                                             | The performance modeling methods                          | 27 |  |  |  |  |  |

|   |                                                                 | 2.3.1 Modular Performance Analysis                        | 28 |  |  |  |  |  |

|   |                                                                 | 2.3.2 Symbolic Timing Analysis for Systems                | 40 |  |  |  |  |  |

|   |                                                                 | 2.3.3 Timed Automata                                      | 42 |  |  |  |  |  |

|   |                                                                 | 2.3.4 Parallel and Object-Oriented Specification Language | 53 |  |  |  |  |  |

|   |                                                                 | 2.3.5 Vienna Development Method                           | 58 |  |  |  |  |  |

|   | 2.4                                                             | Comparing the models                                      | 65 |  |  |  |  |  |

|   | 2.5                                                             | Discussion and conclusions                                | 69 |  |  |  |  |  |

| • |                                                                 |                                                           |    |  |  |  |  |  |

| 3 |                                                                 | ending VDM++ for Distributed Real-Time Systems            | 71 |  |  |  |  |  |

|   | 3.1                                                             | Introduction                                              | 71 |  |  |  |  |  |

|   | 3.2                                                             | The limitations of timed VDM++                            | 72 |  |  |  |  |  |

|   | 3.3                                                             | Proposed changes                                          | 72 |  |  |  |  |  |

|   | 3.4                                                             | Modeling the in-car radio navigation system               | 73 |  |  |  |  |  |

|   |                                                                 | 3.4.1 The environment model                               | 74 |  |  |  |  |  |

|   |                                                                 | 3.4.2 The system model                                    | 76 |  |  |  |  |  |

|   | 3.5                                                             | Abstract Operational Semantics                            | 77 |  |  |  |  |  |

|   |                                                                 | 3.5.1 Syntax and informal semantics                       | 78 |  |  |  |  |  |

|   |                                                                 | 3.5.2 Formal Operational Semantics                        | 79 |  |  |  |  |  |

|   |                                                                 | 3.5.3 Validation                                          | 83 |  |  |  |  |  |

|   | 3.6                                                             | Related work and concluding remarks                       | 84 |  |  |  |  |  |

| 4 | Co-simulation of Distributed Embedded Real-Time Control Systems |                                                           |    |  |  |  |  |  |

|   | 4.1                                                             | Introduction                                              | 85 |  |  |  |  |  |

|   | 4.2                                                             | Current state of practice in academia and industry        | 86 |  |  |  |  |  |

|   | 43                                                              | •                                                         | 88 |  |  |  |  |  |

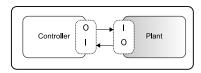

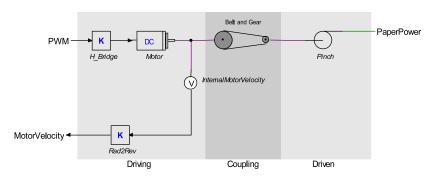

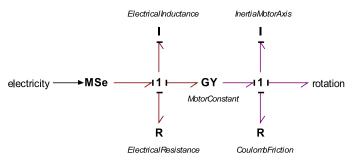

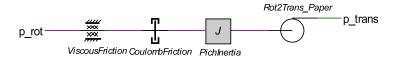

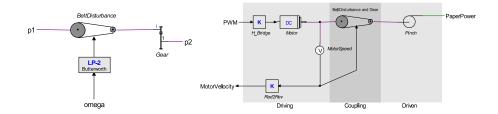

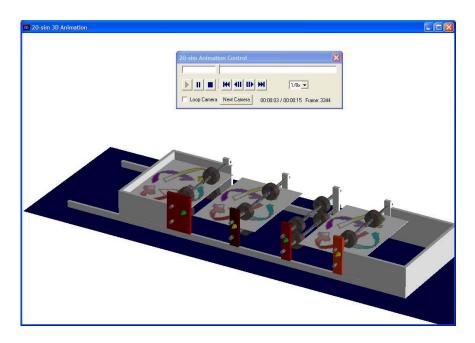

|   |                                 | 4.3.1 Plant modeling                                                                                                                                                                                                                                                                                                                                                                                        | 89                                                                               |

|---|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

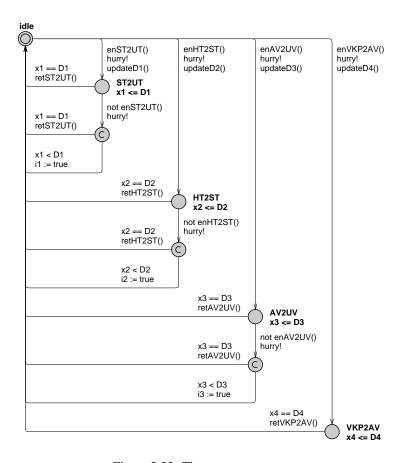

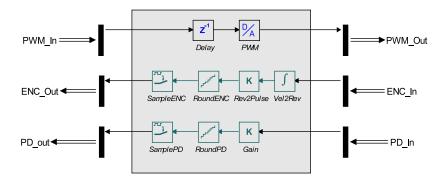

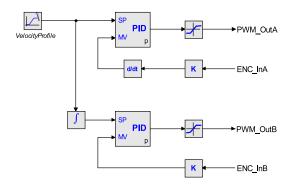

|   |                                 | 4.3.2 Controller description                                                                                                                                                                                                                                                                                                                                                                                | 91                                                                               |

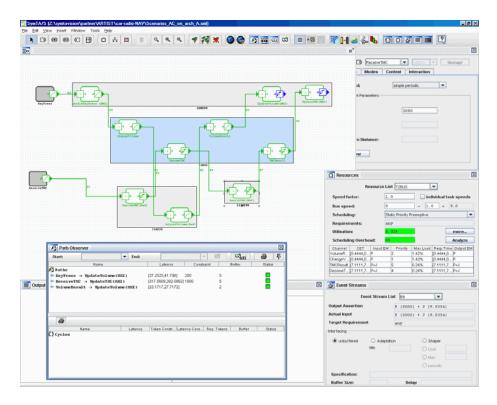

|   | 4.4                             | Tool support                                                                                                                                                                                                                                                                                                                                                                                                | 92                                                                               |

|   | 4.5                             | Reconciled operational semantics                                                                                                                                                                                                                                                                                                                                                                            | 95                                                                               |

|   |                                 | 4.5.1 Syntax and informal semantics revisited                                                                                                                                                                                                                                                                                                                                                               | 96                                                                               |

|   |                                 | 4.5.2 Formal Operational Semantics                                                                                                                                                                                                                                                                                                                                                                          | 98                                                                               |

|   | 4.6                             | Concluding remarks                                                                                                                                                                                                                                                                                                                                                                                          | 104                                                                              |

| 5 | A D                             | evelopment Process for Embedded Control Systems                                                                                                                                                                                                                                                                                                                                                             | 105                                                                              |

|   | 5.1                             | System-level reasoning                                                                                                                                                                                                                                                                                                                                                                                      | 106                                                                              |

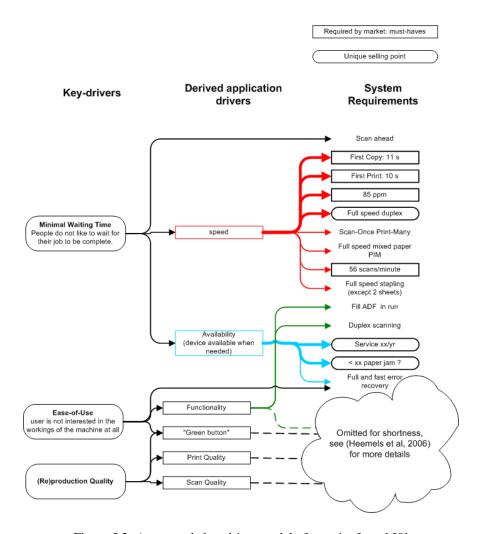

|   |                                 | 5.1.1 The key driver method                                                                                                                                                                                                                                                                                                                                                                                 | 107                                                                              |

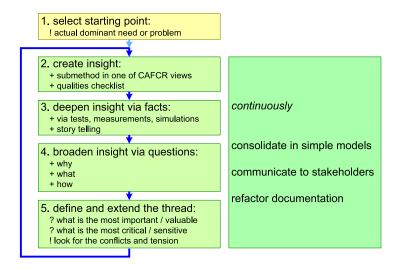

|   |                                 | 5.1.2 Threads of reasoning                                                                                                                                                                                                                                                                                                                                                                                  | 109                                                                              |

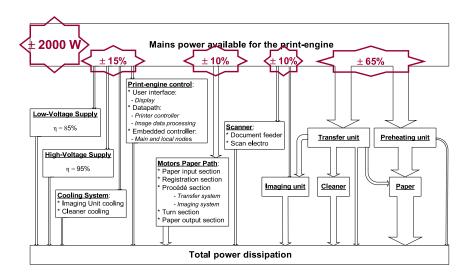

|   |                                 | 5.1.3 Budget-based design                                                                                                                                                                                                                                                                                                                                                                                   | 110                                                                              |

|   |                                 | 5.1.4 From analysis towards design                                                                                                                                                                                                                                                                                                                                                                          | 112                                                                              |

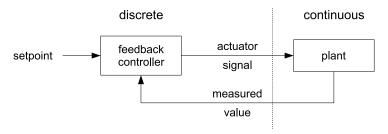

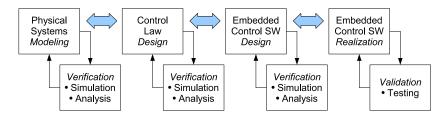

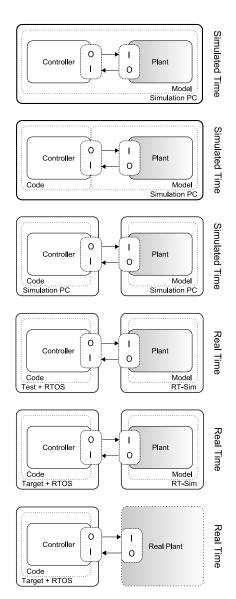

|   | 5.2                             | Control engineering process                                                                                                                                                                                                                                                                                                                                                                                 | 112                                                                              |

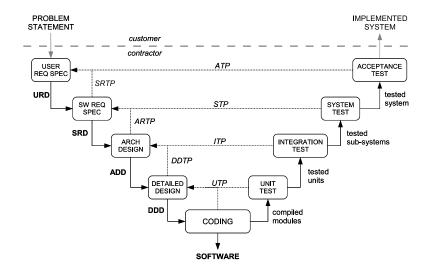

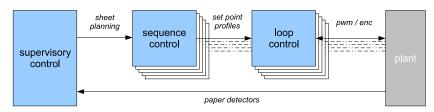

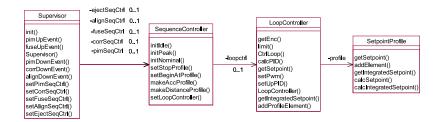

|   | 5.3                             | Software engineering process                                                                                                                                                                                                                                                                                                                                                                                | 115                                                                              |

|   | 5.4                             | Discussion and conclusion                                                                                                                                                                                                                                                                                                                                                                                   | 119                                                                              |

|   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

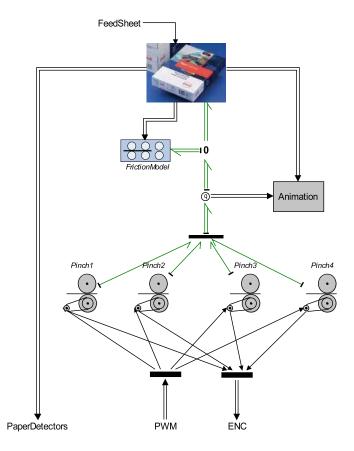

| 6 | Eml                             | bedded Control of a Printer Paper Path - a Case Study                                                                                                                                                                                                                                                                                                                                                       | 121                                                                              |

| 6 | <b>Em</b> l 6.1                 | bedded Control of a Printer Paper Path - a Case Study Introduction                                                                                                                                                                                                                                                                                                                                          | <b>121</b> 121                                                                   |

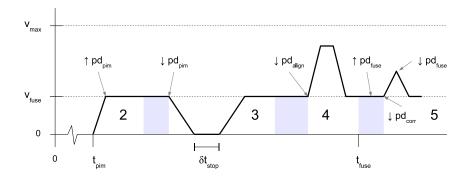

| 6 |                                 | •                                                                                                                                                                                                                                                                                                                                                                                                           | 121<br>124                                                                       |

| 6 | 6.1                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121                                                                              |

| 6 | 6.1<br>6.2                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121<br>124                                                                       |

| 6 | 6.1<br>6.2                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121<br>124<br>128                                                                |

| 6 | 6.1<br>6.2                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121<br>124<br>128<br>129                                                         |

| 6 | 6.1<br>6.2                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121<br>124<br>128<br>129<br>133                                                  |

| 6 | 6.1<br>6.2                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121<br>124<br>128<br>129<br>133<br>134                                           |

| 6 | 6.1<br>6.2<br>6.3               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 121<br>124<br>128<br>129<br>133<br>134<br>144                                    |

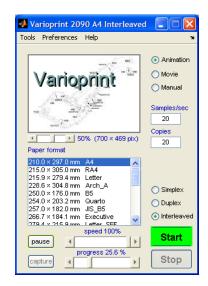

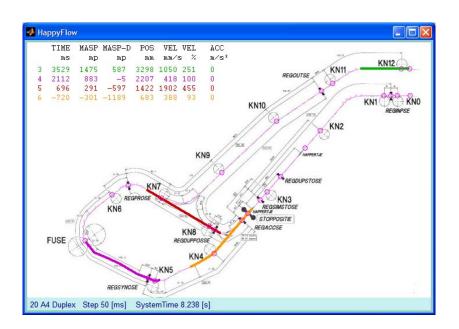

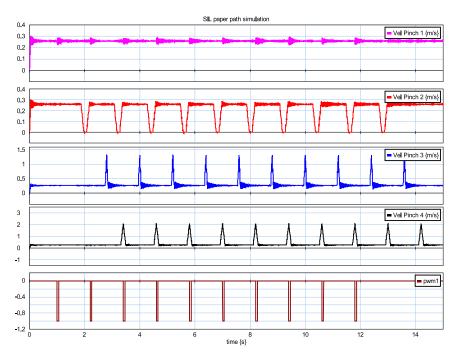

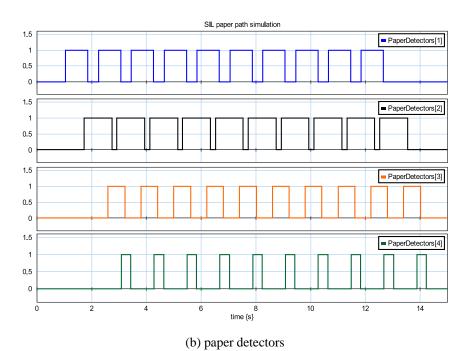

| 6 | 6.1<br>6.2<br>6.3               | Introduction The paper path experimental set-up Modeling the experimental set-up 6.3.1 Modeling the plant 6.3.2 Validating the plant model 6.3.3 Modeling the controller 6.3.4 Validating the controller model Analysis of the simulation results 6.4.1 Co-simulation of the system model 6.4.2 Software-in-the-loop co-simulation                                                                          | 121<br>124<br>128<br>129<br>133<br>134<br>144<br>147                             |

| 6 | 6.1<br>6.2<br>6.3               | Introduction The paper path experimental set-up Modeling the experimental set-up 6.3.1 Modeling the plant 6.3.2 Validating the plant model 6.3.3 Modeling the controller 6.3.4 Validating the controller model Analysis of the simulation results 6.4.1 Co-simulation of the system model 6.4.2 Software-in-the-loop co-simulation 6.4.3 Measurements on the experimental set-up                            | 121<br>124<br>128<br>129<br>133<br>134<br>144<br>147<br>148                      |

| 6 | 6.1<br>6.2<br>6.3               | Introduction The paper path experimental set-up Modeling the experimental set-up 6.3.1 Modeling the plant 6.3.2 Validating the plant model 6.3.3 Modeling the controller 6.3.4 Validating the controller model Analysis of the simulation results 6.4.1 Co-simulation of the system model 6.4.2 Software-in-the-loop co-simulation                                                                          | 121<br>124<br>128<br>129<br>133<br>134<br>144<br>147<br>148                      |

| 6 | 6.1<br>6.2<br>6.3<br>6.4        | Introduction The paper path experimental set-up Modeling the experimental set-up 6.3.1 Modeling the plant 6.3.2 Validating the plant model 6.3.3 Modeling the controller 6.3.4 Validating the controller model Analysis of the simulation results 6.4.1 Co-simulation of the system model 6.4.2 Software-in-the-loop co-simulation 6.4.3 Measurements on the experimental set-up                            | 121<br>124<br>128<br>129<br>133<br>134<br>144<br>147<br>148<br>149<br>150        |

|   | 6.1<br>6.2<br>6.3<br>6.4        | Introduction The paper path experimental set-up Modeling the experimental set-up 6.3.1 Modeling the plant 6.3.2 Validating the plant model 6.3.3 Modeling the controller 6.3.4 Validating the controller model Analysis of the simulation results 6.4.1 Co-simulation of the system model 6.4.2 Software-in-the-loop co-simulation 6.4.3 Measurements on the experimental set-up Discussion and conclusions | 121<br>124<br>128<br>129<br>133<br>134<br>144<br>147<br>148<br>149<br>150<br>153 |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Introduction The paper path experimental set-up Modeling the experimental set-up 6.3.1 Modeling the plant 6.3.2 Validating the plant model 6.3.3 Modeling the controller 6.3.4 Validating the controller model Analysis of the simulation results 6.4.1 Co-simulation of the system model 6.4.2 Software-in-the-loop co-simulation 6.4.3 Measurements on the experimental set-up Discussion and Coutlook    | 121<br>124<br>128<br>129<br>133<br>134<br>144<br>147<br>148<br>149<br>150<br>153 |

# **Chapter 1**

# Introduction

Computers are all around us and we use them every day, sometimes even without giving it a second thought. The term "computer" often refers to the personal computer (PC), which is used to send e-mail and browse the Internet or perhaps a video game console that is used for entertainment. But computers are also part of the alarm clock, coffee machine, dishwasher, video recorder, DVD player, photo camera, television set and mobile telephone. This class of systems is often referred to as "embedded systems". Wikipedia defines an embedded system <sup>1</sup> as: "a special-purpose system in which the computer is completely encapsulated by the device it controls". Corporaal observes in a recent white paper [20] that you can easily count up to a hundred embedded devices in an average family household nowadays.

We become more and more dependent on the proper operation of these embedded systems. Not only because they are efficient and convenient to use but also because they potentially affect the quality of life. Sangiovanni-Vincentelli mentioned in his presentation [89] at the 2006 Design Automation and Test in Europe (DATE) conference that a modern, high-end, car contains 80 microprocessors executing several million lines of code. These microprocessors are used to control not only the car radio and air conditioning, but also the air bag, cruise control, fuel injection, brakes and power steering. A failure in any one of those critical embedded systems may have severe consequences. But the general public is typically not aware of this, because these computers are deeply embedded in the system, hidden well out of plain sight. Dependability issues are typically associated with the military, medical or aeronautical domains but not so much with consumer or capital goods. For example, does one ask about the code coverage statistics of the power steering unit (an embedded system that contains a microprocessor which executes possibly several thousands lines of code) when you buy a new car? In 2004, Deutsche Welle reported <sup>2</sup> that the reliability rating of German cars, which used to be unrivalled and universally acclaimed, has been steadily decreasing for several years in succession as compared to their main competitors. Analysts believe that this may very well be due to the increased complexity as outlined by Sangiovanni-Vincentelli.

The impact of embedded systems is likely to grow even far beyond what is possible today. The on-going miniaturization and wireless digital communication has made mobile computing already a reality. We have seen the desktop PC shrink, first to a laptop and then to a personal digital assistant (PDA) in less than a decade, without a

<sup>&</sup>lt;sup>1</sup>See http://en.wikipedia.org/wiki/Embedded\_systems

<sup>&</sup>lt;sup>2</sup>See http://www.dw-world.de/dw/article/0,2144,1400331,00.html

significant loss in performance. Personal audio systems, like Apple's iPod, are now common place. In principle, you can reach any one, at any place, at any time. The growth in application areas seems to be limited only by the amount of power such a mobile device requires. Visionaries claim that we will be moving towards *ubiquitous computing* <sup>3</sup>, a paradigm whereby the distinction between computers and their environment will eventually disappear completely. Advocates like Aarts [1] also refer to this as "ambient intelligence". Companies such as Philips <sup>4</sup> already demonstrate that this is not just science fiction. They are building actual prototypes of products for the consumer, lighting and medical markets based on these ideas in their ExperienceLab.

The economic relevance of embedded systems is easily demonstrated. For example, take mobile telephony. Market analysts such as Informa Telecoms & Media <sup>5</sup> predicted in 2005 that the number of mobile hand-sets deployed world-wide would reach 1 billion early in 2007 which corresponds to roughly twenty percent of the population on Earth! Moreover, this target was reached in just fifteen years and the market is far from saturated. Growth is expected to continue by at least ten percent per year until 2012. These numbers are just staggering and it is obvious that such a market potential generates an enormous amount of pressure on the companies that build these kinds of products. Production volumes are extremely high, profit margins are typically low which implies that you have to reach the market with a new product before your competitor, in order to be economically successful. This so-called "time-to-market" (TTM) pressure is therefore the beast to beat.

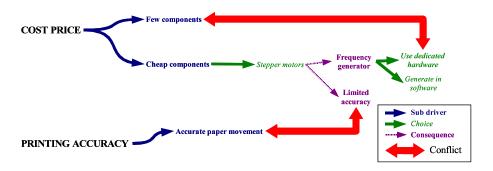

Companies invest huge amounts of money and effort in order to reduce the production time and cost-price of their products. This has created a secondary economy consisting of companies that deliver (half-) products and services to achieve those goals. For example, Gartner <sup>6</sup> reports that the revenues for electronic design automation (EDA) will experience double-digit growth in 2006, reaching 4.5 billion US Dollar. But do all these investments lead to good products? Unfortunately not. It seems that the well-known adage "*Price, Time, Quality - Pick Any Two for Success*" is still a fact of life, as is shown in Figure 1.1.

After the famous CHAOS report from the Standish Group <sup>7</sup> appeared in 1994, there have been numerous published examples of projects failing or products malfunctioning. Despite efforts to improve the quality of computerized systems, it remains difficult to make error-free systems. Most surprisingly, end-users seem to have accepted that as a given fact. People are used to reboot their computer if a problem occurs. If it does not work, you just download the latest software from the web-site. Updates and upgrades have become part of the business model of the product. Even more so, only limited warranties <sup>8</sup> are provided and companies typically do not accept any liability from the use of their products. Would you buy a car if you would have to sign such a legal document? Open source software comes with a so-called "as-is" disclaimer, without warranty of any kind. The GNU General Public License <sup>9</sup> actually contains the following sentence: "The entire risk as to the quality and performance of the program is with you." Yet, open source software is often believed to be of higher quality than most commercial software, because it is exposed to public scrutiny.

<sup>&</sup>lt;sup>3</sup>See http://en.wikipedia.org/wiki/Ubiquitous\_computing

<sup>&</sup>lt;sup>4</sup>See http://www.research.philips.com/

<sup>&</sup>lt;sup>5</sup>See http://www.informatm.com

<sup>&</sup>lt;sup>6</sup>See http://www.gartner.com, Doc. Id. G00143619

<sup>&</sup>lt;sup>7</sup>See http://www.standishgroup.com/sample\_research/chaos\_1994\_1.php

<sup>&</sup>lt;sup>8</sup>See for example the End-User Licence Agreement at http://www.microsoft.com.

<sup>&</sup>lt;sup>9</sup>See http://gplv3.fsf.org.

Figure 1.1: Decision making at large: how to find the optimum?

Quality is a major issue in embedded systems development, mainly because of the production volumes involved. Intel Corporation was forced to recall a substantial number of their early Pentium processors in 1994 because a problem was found in the floating point unit after the product release. Harrison reported at the 2005 ForTIA Industry Day [72] that Intel wrote off 475 million Dollar because of the Pentium FDIV bug and suffered considerable damage to their reputation. But even in a low-volume market things can go spectacularly wrong with great consequences. On June 4, 1996, the inaugural flight of the Ariane-5 rocket failed. About 40 seconds after initiation of the flight sequence, at an altitude of about 3700 m, the launcher veered off its flight path, broke up and exploded. The Cluster mission, consisting of four identical scientific satellites, was lost during this event. Conservative estimates suggest that this accident costed the European tax payer in the order of 300 million Euro. The Inertial Reference System (abbreviated in French: SRI), which is used to determine the attitude of the launcher, shut down mid flight because an exception occurred in the software calculating the current flight path. Virtually the same system had been used to launch Ariane-4 rockets successfully for many years, but it was used outside its original specification in this particular case. The investigation showed that the system was never tested under flight conditions despite suggestions from the responsible engineers. In fact, the Ariane-5 Accident Report [71] states: "... it was jointly agreed not to include the Ariane-5 trajectory data in the SRI requirements and specification.". However, the report does not state why this decision was made. It is commonly believed that the time-to-market pressure, to have this new generation launcher operational as soon as possible, may have contributed to this decision, taking into account the excellent track-record of a similar system on Ariane-4. Johnson reports on similar problems at NASA in [59]. The "Faster, Better, Cheaper" initiative, which was announced in 1998, fostered a culture in which engineers took considerable risks to innovate with new design in order to meet requirements. In hindsight, time-to-market is one of the contributing factors [10] to the loss of the Mars Polar Lander mission in 1999.

## 1.1 The embedded systems design challenge

One might argue that the examples mentioned above are somewhat dated and do not reflect the current state of practice. But in fact, Johnson has demonstrated in [60] that the average likelihood of projects succeeding has only *marginally improved* over the last decade, despite substantial investments in tools and processes. It is generally believed that the performance in the embedded systems domain is rather worse than better. Why is this the case? Looking at general trends there are a few potential reasons.

The design gap problem. According to Moore's Law [74], the performance of hardware is roughly doubled every eighteen months. But recent advances in networking, packaging and integration technology has enabled the development of heterogeneous embedded computing platforms that show a potential exponential growth in performance and thus complexity [58]. These platforms are commonly referred to as System-On-Chip or Network-On-Chip and usually combine multiple and interconnected radio-frequency, analog and digital components on a single chip. However, the technology we use to design the applications for these new platforms cannot keep up with this tremendous growth in capabilities, primarily because they are currently focused on designing single, monolithic systems. In other words, the complexity of the problem grows much faster than the capabilities of today's leading design tools. This is commonly referred to as the "design gap".

The moving target problem. Rapidly evolving technology and the constant quest for reducing cost-price forces designers of embedded systems to operate on the edge of what is technically feasible. In order to stay competitive they sometimes need to adopt novel technology even while a product is already under development. One of the key problems in embedded systems design is the *validation* of these design decisions. How much effort and time does it take to check that the intent of a design choice works out in practice? Over-dimensioning is the usual approach to accommodate for uncertainty in the design but this is typically not economically viable because it increases the cost price. Sometimes actual prototypes need to be built in order to assess the feasibility of some potential solution. Managing this process is regarded as the key to success and it is often referred to as "shooting at a moving target".

The requirement versus design paradox. Making design decisions in the early phases of the system life-cycle is notoriously difficult. In this stage, requirements are often unclear and under-specified, at best leading to a long list of properties that the system shall eventually satisfy. In the past, emphasis has been put on managing the requirements process, such that sufficient information is available at the time the design decisions are made. However this is often not realistic, in particular in the domain of embedded systems. At the time when requirements are elaborated, the major architectural design decisions also need to be taken, primarily in order to meet the time-to-market target for the product. But how can one make these crucial decisions when there is still so much uncertainty? This is in particular true for performance criteria that the system must meet because they are in general surprisingly hard to quantify and evaluate. It is obvious that elaboration of the requirements is guided by the chosen architecture but in turn the definition of the architecture depends on clear and unambiguous requirements. System architects have to deal with this paradox, for example by applying iterative development processes in order to close the design loop.

Multi-disciplinary design. Systems are traditionally designed in a mono-disciplinary style usually with an organizational structure to reflect this (e.g. mechanical department, electronics department, software department and so on). While in the past systems where developed out-of-phase (mechanical design precedes electrical design which in turn precedes software design) nowadays concurrent engineering is applied in order to save development time. However, system-level requirements that cannot be assigned to a single discipline, such as performance, typically cause great problems during the integration phase because the responsibility to meet the requirement is shared among all disciplines. The root cause of this problem is the lack of crossdiscipline design interaction. This problem cannot be solved by improving the internal organization; the way (embedded) software is currently being developed is fundamentally different from, for example, mechanical and electrical design. These engineers basically speak a different language, are concerned about different types of problems and use different techniques to address and solve these problems. This challenge is dominant in the embedded systems domain because the computer and the device it controls both loose their function if they were to be separated. Hence, they cannot be designed in isolation which makes the cross-discipline communication mandatory.

## 1.2 The BODERC research project

The issues listed in the previous section played an important role in defining the objectives for a new research project at the Embedded Systems Institute (ESI) in the summer of 2002. The central idea was to explore model-based engineering as a methodology for the design and analysis of high-tech systems. It was believed that: "the product creation time can be reduced significantly by the use of multi-disciplinary models during the early product development phases" [47]. The project should therefore bring researchers from different engineering disciplines and industrial practitioners together in an "Industry as a Laboratory" setting [82]. Océ Technologies <sup>10</sup>, a leading manufacturer of high-volume document printing systems, became the so-called carrying industrial partner or "problem statement owner" in the project. Océ and ESI spearheaded a consortium consisting of the companies Imtech and Chess and researchers from the Technical University of Eindhoven, Radboud University Nijmegen and the University of Twente. The project was partially financially supported by the Netherlands Ministry of Economic Affairs under the Senter TS program.

The difficulty of multi-disciplinary research was already demonstrated during the definition phase of the project. The participants were unable to reach an agreement on the definition of the term "model". Each discipline seemed to have its own definition that was incompatible with what others used. The debate continued until one of the participants observed that Bo Derek, the famous movie actress, is also a model and this point was of course conceded quickly. It actually inspired the name of the project: BODERC, which is an acronym that stands for "Beyond the Ordinary: Design of Embedded Real-time Control". The project was started in September 2002 and was completed in March 2007.

High-tech mechatronic systems, such as high-volume printers, are complex and so is the associated design process. Many implementation choices need to be made and the impact of each decision is difficult to assess due to this inherent complexity. This makes the design process error prone and vulnerable to failure as other downstream design

<sup>&</sup>lt;sup>10</sup>See http://www.oce.com.

choices may be based on it, causing a cascade of potential problems. Moreover, it may take some time to realize that a decision is wrong because it will require feedback in the design process. Usually this happens at system integration and testing or product manufacturing. The repairs required to fix these problems cause significant project delays and cost overruns or sometimes even worse: product cancelation. Three reasons are identified in the BODERC project that seem to be the root cause of this problem and they are listed here for convenience:

- Reasoning about system-level properties is difficult because a common language

is lacking. Each engineering discipline uses its own method, vocabulary and

style of reporting. This incompatibility causes confusion often leading to misunderstandings and wrong assumptions being made on the sub-designs of other

disciplines. These inconsistencies are hard to spot because there is usually no

structured system design reasoning process in place.

- 2. Many design choices are made implicitly, usually based on previous experience, intuition or even assumptions. System-level reasoning is made difficult if the rationale behind such a decision is not quantified. The reasons are sometimes kept hidden on purpose, for example if strong personal preference or politics plays a role. This may perhaps lead to a local optimum in the system design but only rarely to a global optimum. It is therefore necessary to make design knowledge explicit in order to enable the dialogue at the system level.

- Dynamic or time dependent aspects of a system are complex to grasp and more over, there are not many methods and tools available to support reasoning about time varying aspects in design, in contrast to static or steady-state aspects.

The effects of the above mentioned points are amplified by the complexity of the product under development (a high-volume printer typically consists of tens of thousands of components and millions lines of code) and the complexity of the design process (number of people involved, organizational structure, out-of-phase or multisite development, etcetera). The hypothesis of the project is that light-weight models that capture the system-level behavior and a reasoning method that indicates how and when to use them will release the aforementioned tension considerably. A good system engineering methodology shall expose implicit or hidden design choices and replace the usual "hand-waving" by design rationale which is based on objective, quantified and verifiable information.

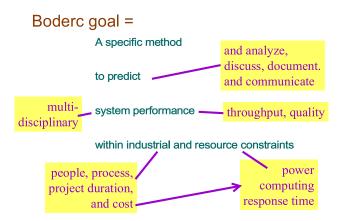

The goal of the BODERC project is graphically presented in Figure 1.2. The aim is to develop a model-based methodology that supports multi-disciplinary design (space exploration) by predicting system performance. The developed models, methods and techniques shall be applicable in the early design phases and must satisfy industrial application constraints. Hence, the methodology shall be usable in an industrial context with its particular people, organization and constraints such as product and process legacy, time, effort and money.

## 1.3 The goal of this thesis

The aim of this thesis is to define a method that supports the multi-disciplinary design of embedded systems. This is obviously a broad field, therefore we focus on the scope set by the BODERC project definition: the design of distributed real-time control systems. Furthermore, a number of challenging sub-goals were defined:

Figure 1.2: The BODERC research project goal from [47]

- 1. The method shall be able to address design problems at the system level; these are so-called cross-cutting concerns that usually affect more than one engineering discipline such as performance and dependability.

- 2. The method shall be able to predict whether or not both the functional and extrafunctional properties are satisfied by the proposed system architecture.

- 3. The method shall provide means of abstraction that are appropriate for modeling the problem at hand; this may require support for different levels of abstraction for different parts of the problem but from within a single framework.

- 4. The method shall be cost effective; the amount of effort invested in modeling should be balanced with the insight gained from the analysis.

- 5. The method shall be easy to adopt for the average engineer currently working in the field at acceptable initial investment.

The overall aim is to be able to address industrial size problems, whereby the "grand challenge" is modeling and analysis of the paper path of a high-volume printer. The goal of this thesis is to investigate whether or not a method exists, or can be defined, that satisfies the requirements listed above, whereby its overall effectiveness is studied and demonstrated on this industrial case study.

## 1.4 Organization of this thesis

The first part of this thesis looks at several state-of-the-art performance evaluation methods and tools. The aim of the exercise is to understand the capabilities and limits of those methods by applying them on the same case study. Modular Performance Analysis (MPA), Symbolic Timing Analysis for Systems (SymTA/S), Parallel Object-Oriented Specification Language (POOSL), Timed Automata and the Vienna Development Method (VDM) are used to model and analyze an in-car radio navigation system. The result of this comparison is presented in Chapter 2 and it is based on the following publications:

- [105] Ernesto Wandeler, Lothar Thiele, Marcel Verhoef and Paul Lieverse. System Architecture Evaluation using Modular Performance Analysis A Case Study. Appeared in International Journal of Software Tools for Technology Transfer (STTT), Volume 8, No 6, pages 649-667. Springer, 2006. This is an extended version of the research paper that was published at the First International Symposium On Leveraging Applications of Formal Methods ISOLA 2004.

- [51] Martijn Hendriks and Marcel Verhoef. Timed Automata Based Analysis of Embedded Systems Architectures. Appeared in the proceedings of 20<sup>th</sup> International Parallel and Distributed Processing Symposium IPDPS 2006, Workshop on Parallel and Distributed Real-Time Systems WPDRTS. IEEE, 2006.

- [34] Oana Florescu, Jeroen Voeten, Marcel Verhoef and Henk Corporaal. *Reusing Real-Time Systems Design Experience Through Modelling Patterns*. Chapter in *Advances in Design and Specification Languages for Embedded Systems*. Selected papers FDL 2006 (best paper award). pages 329-348. Springer, 2007.

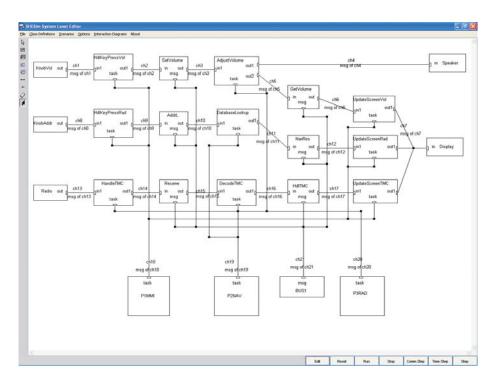

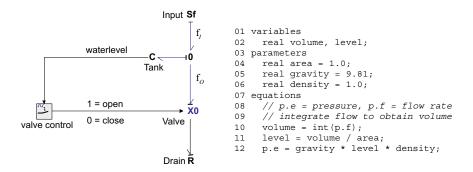

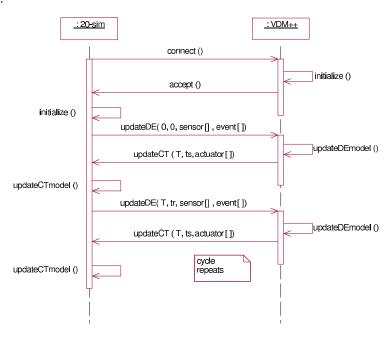

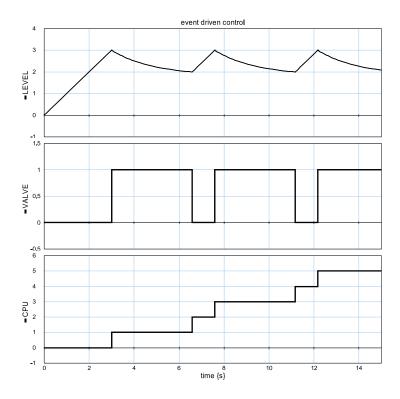

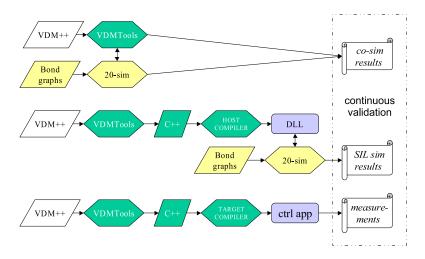

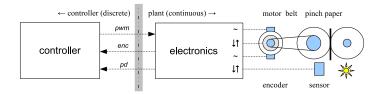

The second part of this thesis addresses the concerns identified during the comparison. Method improvements are proposed and implemented. Small case studies are used to check the upgraded tool support. Timed VDM++ is extended with asynchronous operations and an explicit notion of system architecture in Chapter 3. The semantics of these language extensions are defined and the implemented tool support is again applied to the in-car radio navigation case study. The improved VDM++ notation is coupled to 20-SIM, a dynamic systems modeling and simulation environment in Chapter 4. The semantics of both methods is reconciled and the integrated tools are applied to a case study: a water tank level controller. The results presented are based on the following publications:

- [101] Marcel Verhoef, Peter Gorm Larsen and Jozef Hooman. *Modeling and Validating Distributed Embedded Real-Time Systems with VDM++*. Appeared in the proceedings of *FM 2006: Formal Methods*. LNCS 4085, pages 147-162. Springer, 2006.

- [102] Marcel Verhoef, Peter Visser, Jozef Hooman and Jan Broenink. Co-simulation of Real-Time Embedded Control Systems. Appeared in the proceedings of Integrated Formal Methods. LNCS 4591, pages 639-658. Springer, 2007.

- [56] Jozef Hooman and Marcel Verhoef. Formal Semantics of a VDM Extension for Distributed Embedded Systems. Paper included in festschrift to honor professor Willem-Paul de Roever. In Correctness, Concurrency and Compositionality. LNCS Festschrift Series, Springer, 2008 (to appear).

The third part of this thesis puts these results back into the industrial context. Both the embedding of the methods and tools in an industrial design process is considered in Chapter 5 and their application to the "grand challenge" of this thesis in Chapter 6: the printer paper path. And, last but not least, the result of this research work is discussed and evaluated in Chapter 7. This work is based on the following publications:

[88] Heico Sandee, Maurice Heemels, Gerrit Muller, Peter van den Bosch, Marcel Verhoef. *Threads of Reasoning: A Case Study in Printer Control*. Appeared in the proceedings of the 16<sup>th</sup> Annual International INCOSE Symposium. International Council on Systems Engineering, 2006.

- [32] John Fitzgerald, Peter Gorm Larsen, Simon Tjell, Marcel Verhoef. *Validation Support for Distributed Real-Time Embedded Systems in VDM++*. Appeared in the proceedings of the 10<sup>th</sup> IEEE High Assurance Systems Engineering Symposium, pages 331-340. IEEE, 2007.

- [4] Zoe Andrews, John Fitzgerald, Marcel Verhoef. Resilience Modeling Through Discrete Event and Continuous Time Co-simulation. Extended abstract appeared in the proceedings of the 37<sup>th</sup> Annual IEEE/IFIP International Conference on Dependable Systems and Networks. IEEE, 2007.

## Other publications

Several related published works are not included in this thesis:

- [96] Peter van den Bosch, Gerrit Muller, Marcel Verhoef and Oana Florescu. Modeling of Hardware Software Performance in High-Tech Systems. Appeared in the proceedings of the 17<sup>th</sup> Annual International INCOSE Symposium. International Council on Systems Engineering, 2007.

- [100] Marcel Verhoef and Peter Gorm Larsen. *Interpreting Distributed System Architectures Using VDM*++. Appeared in the proceedings of the 5<sup>th</sup> Conference on System Engineering Research. Stevens Institute of Technology, 2007.

- [30] John Fitzgerald, Peter Gorm Larsen, Paul Mukherjee, Nico Plat and Marcel Verhoef. Validated Designs for Object-Oriented Systems. ISBN 1-85233-881-4. Springer, 2005, 402 pages.

- [99] Marcel Verhoef and Jozef Hooman. *Evaluating Embedded Systems Architectures*. Summary of Chapter 2 from this thesis which appeared in the BODERC final report [47]. Pages 151-160. ESI, 2006.

- [95] Peter van den Bosch, Oana Florescu, Marcel Verhoef and Gerrit Muller. *Modeling of performance*. Chapter in the BODERC final report [47]. Pages 101-114. ESI, 2006.

- [72] Tiziana Margaria, Bernhard Schätz, Marcel Verhoef. Formal Methods Going Mainstream: Costs, Benefits, Experiences. Report on the ForTIA Industry Day at FM 2005. Appeared in the BCS FACS Newsletter Issue 2006-2, pages 34-38. British Computer Society, 2006.

- [98] Marcel Verhoef. *On the use of VDM++ for Specifying Real-time Systems*. Appeared in the proceedings of the First Overture Workshop at FM 2005, Technical Report CS-TR-969, pages 26-43. Newcastle University, 2006.

# Chapter 2

# **Evaluating Embedded System Architectures**

### 2.1 Introduction

An architectural description of a product is typically made during the initial phases of an industrial product creation process. For example, an *Operational Concept Description* document from the IEEE 12.207 system life cycle standard may be produced. Such a document does not only list functional and extra-functional requirements, boundary conditions and other restrictions for the design, but it also contains high-level Use-Cases. These Use-Cases, or scenarios, describe how the system is typically used and they are the starting point for the design of the embedded system architecture. Although there is no principle limit to the number of scenarios that can be analyzed, it is not uncommon to first concentrate on those Use-Cases that have the highest expected impact on the set of target system-level requirements. It is the system architect who makes this selection, often based on previous experience. Quantitative performance analysis can be used to guide the design process.

However, when a new system is being developed, there is typically little quantitative data available to work with. Therefore, course grain assumptions are used initially. Typically, these values are "guestimates" or extrapolated performance figures obtained from systems developed previously. During the design and development phases, the system architect will constantly try to improve the accuracy of the models by using for example better estimation techniques on details of the design, such as worst-case execution time analysis of existing or new source code, by benchmarking new critical system components on the target hardware or by performing measurements on existing and comparable systems. It is clear that performance analysis is an activity that needs to be performed throughout the system life cycle, in particular because requirements are likely to change over time.

In this chapter, we investigate several techniques that can be used to evaluate performance properties of embedded system architectures such as latency, throughput and resource utilization. We focus on these properties in particular, because they play a significant role in the selection of a suitable embedded architecture. The challenge is to decide, at design time:

- which of the proposed architectures is best suited, or,

- how to distribute functionality on a proposed embedded architecture, or,

- how to select suitable architecture parameters,

such that required performance targets and cost levels are met. This is often a trade-off between competing or even adversary requirements. Performance analysis techniques can be used to expose these design conflicts. This is demonstrated in this chapter by applying five different techniques to a common case study. These techniques are: Modular Performance Analysis (MPA), Symbolic Timing Analysis for Systems (SymTA/S), Timed Automata, the Parallel Object-Oriented Specification Language (POOSL) and the Vienna Development Method (VDM++). The aim of the experiment is to better understand the capabilities and limits of each method and to determine the value of the predictions derived from each model. It is certainly not the intent to determine which method is best. The experiment is too small and it has not been executed under controlled circumstances. The comparison was performed during the ARTIST2 workshop held at the Lorentz Center at Leiden University (November 2005) where experts on the relevant techniques where challenged to attack a common set of problems <sup>1</sup>. The case study described in the next section, which was originally used for an early version of [105], was put forward by the author of this thesis. The scope of the comparison presented here is limited to those techniques that were represented at the workshop.

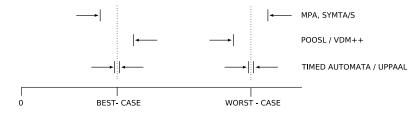

Some interesting observations can be drawn from the comparison because the five techniques and their associated tools are very different. MPA is based on a deterministic queuing theory and uses Matlab as a front-end to compose and analyze abstract performance models extremely efficiently. SymTA/S combines deterministic queuing theory with classical scheduling theory to build abstract performance models using a nice and intuitive user interface. MPA and SymTA/S both provide hard, but not necessarily tight, results. Timed Automata is a general purpose modeling framework that can be analyzed using the UPPAAL model checker, possibly leading to accurate results. POOSL and VDM++ belong to the class of formal modeling languages that can be subjected to rigorous analysis techniques such as interactive theorem proving and model checking. However, discrete event simulation is used to analyze the POOSL and VDM++ models here. While MPA and SymTA/S abstract away from the actual computation that is performed by the system, Timed Automata, POOSL and VDM++ allow to describe the system functionality in more detail.

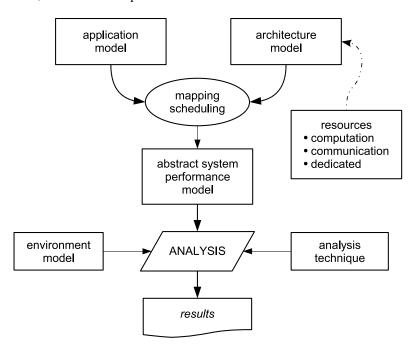

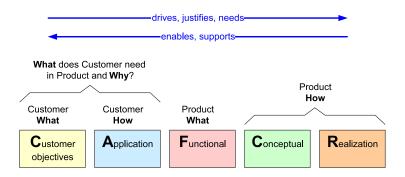

The well-known Y-chart, as proposed by Kienhuis et al in [62] and shown in Figure 2.1, is used as a framework for our comparison. The central idea of the Y-chart, which is not specific to any performance analysis technique in particular, is to build an abstract model of the concrete system that bundles all information needed for performance analysis. The following steps are taken to construct a Y-chart model:

- 1. identify key usage scenarios and system functions and quantify event rates, message sizes and execution times;

- 2. identify resources and their communication structure and quantify resource and communication capacities;

- 3. compose a system model, calculate (or simulate) and evaluate.

<sup>&</sup>lt;sup>1</sup>The problem set can be found at http://www.tik.ee.ethz.ch/~leiden05

The model resulting from steps 1 and 2 unifies essential information about the environment, about the available computation and communication resources, about the application tasks (or dedicated HW/SW components), as well as the system architecture itself. First, the Y-chart is explained in more detail.

Figure 2.1: The Y-chart method for performance analysis

The application model (top-left in Figure 2.1) provides an abstract definition of the software or application logic that needs to run on the system. Application specific performance requirements are usually specified in this model. We will demonstrate how annotated UML sequence diagrams can be used to represent application models.

The architecture model (top-right in Figure 2.1) defines on which hardware the application(s) shall be deployed. It describes which computation resources (such as microprocessors) are available and how they are interconnected using communication resources (such as buses). The architecture model is typically composed from a library of well-defined standard resources (middle-right in Figure 2.1). These resource models provide information about the properties of the generic computing and communication resources that are available, such as processor speed and communication bus bandwidth. This information is typically found in data sheets or benchmarks, or can be obtained from measurements on existing systems. This library might also contain black-box descriptions of highly specialized components that are used for some dedicated task in the system, e.g. an encryption device.

The abstract system performance model is constructed by describing the deployment of the application model (the software) on the architecture model (the hardware, indicated as the so-called "mapping" in Figure 2.1). Furthermore, architecture parameters, such as the type of scheduling or arbitration used on each resource, are specified in this model. UML deployment diagrams or AADL models may be used to describe the mapping, but in this chapter we use an intuitive informal approach for deployment.

The environment model (bottom-left in Figure 2.1) defines the interface between the system and the surrounding environment. It describes for example how often system functions will be called, how much data is provided as input to the system and so on. Typically, end-to-end system-level requirements are specified in environment models. Environment models can, for example, be derived from measurements or traces.

The suitability of the proposed system architecture can be determined once the abstract system performance model has been evaluated with a certain technique in step 3. This is often difficult due to adversary requirements, such as for example cost price versus performance. Typically, a set of near-optimal solutions exists which requires heuristics for the "final" decision making. However, the process needs to be repeated if one of the requirements is clearly not met. This usually requires changing the application model (e.g. improve the algorithm to reduce processor load) or changing the architecture model (e.g. select a faster processor or bus) or changing the mapping (e.g. reallocate applications to different computation resources). This process is repeated until all requirements are met. This evaluation approach is commonly referred to as system-level performance optimization or, when higher levels of automation are involved, design space exploration. Note that it is not just restricted to performance requirements in the narrow sense used here. Other aspects that influence the choice of architecture, such as power usage, may also be taken into account.

First, the application and architecture models are presented in Section 2.2.1 and the environment model is defined in Section 2.2.2. Then, in sections 2.3.1 - 2.3.5, the modeling techniques are introduced. And finally, the results and lessons learned from the case study are discussed in Section 2.4.

## 2.2 The In-Car Radio Navigation system case study

The case study presented in this section is inspired by a system architecture definition study for a distributed in-car radio navigation system. Such a system typically executes a number of concurrent applications that share a common platform. Nevertheless, each application has individual performance requirements that need to be met by the platform. During the system definition phase, several candidate platform architectures might be proposed by the engineers and the system architect needs to evaluate each one and decide which one to implement. First, the system sub-model is presented in Section 2.2.1 and the environment sub-model is presented in Section 2.2.2.

### 2.2.1 Modeling the system

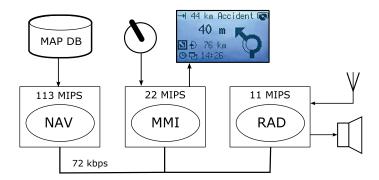

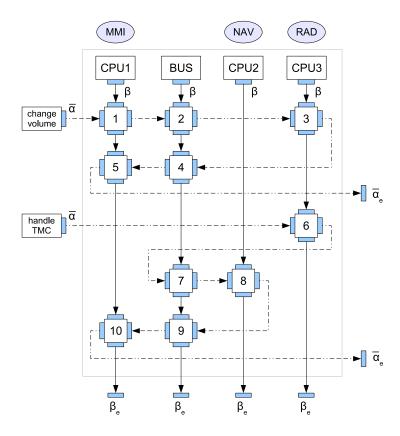

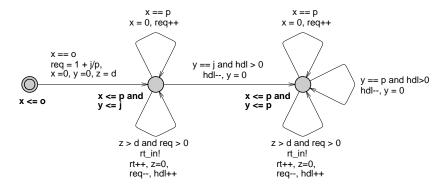

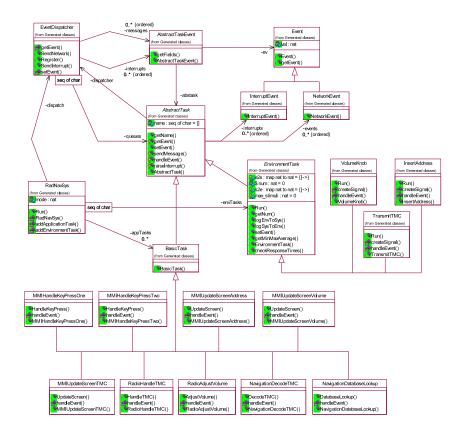

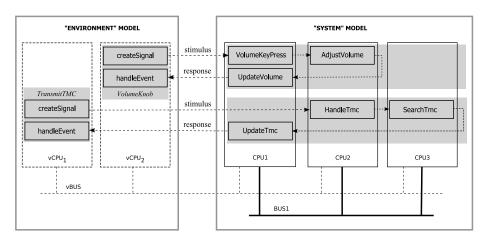

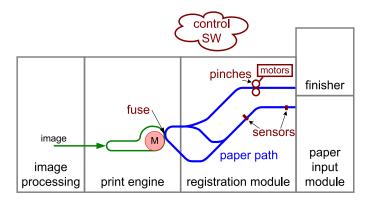

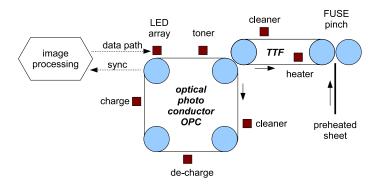

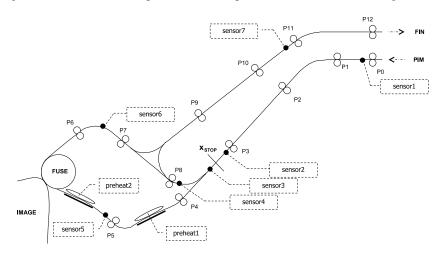

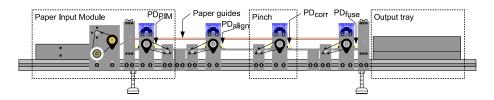

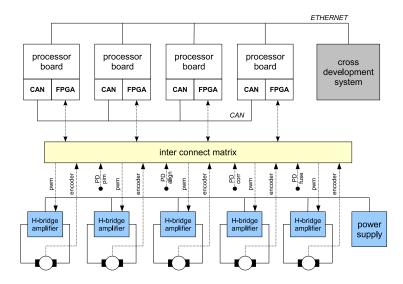

An overview of the system is presented in Figure 2.2. It is composed of three main clusters of functionality:

- The man-machine interface (MMI) which takes care of all interaction with the user, such as handling key inputs and graphical display output.

- The navigation functionality (NAV) which is responsible for destination entry, route planning and turn-by-turn route guidance giving the driver both audible and visual advices. The navigation functionality relies on the availability of a map database, typically stored on a CD or DVD, and positioning information, e.g. speed and GPS. The positioning sensors are not shown and considered here.

- The radio functionality (RAD) which is responsible for basic tuner and volume control as well as handling of traffic information services such as RDS TMC

(Radio Data System / Traffic Message Channel). RDS TMC (or TMC for short) is broadcast along with the audio signal of radio channels.

Figure 2.2: High-level overview of a distributed radio navigation system

### Step 1 of the Y-chart approach - scenario inventory

In our case study, we have selected three distinctive Use-Cases or scenarios:

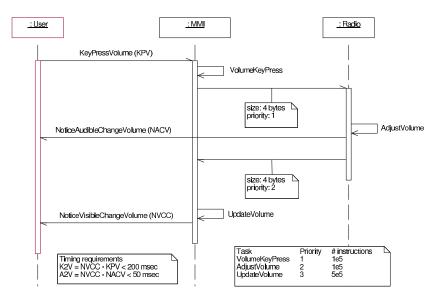

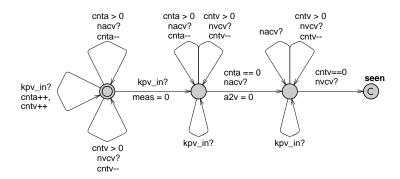

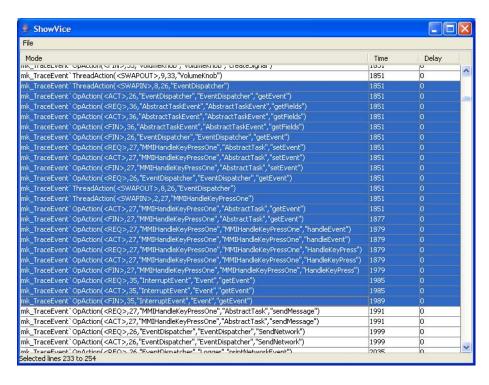

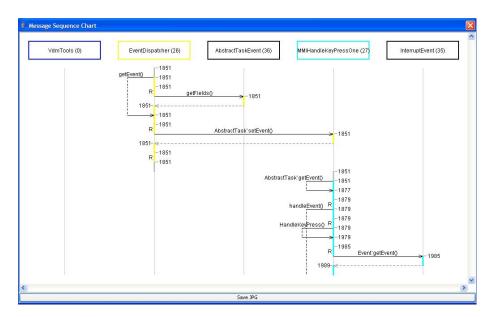

- 1. "Change Volume" The user turns the rotary button and expects near instantaneous audible feedback from the system. Furthermore, the visual feedback (the volume setting on the screen) should be timely and synchronized with the audible feedback. This seemingly trivial Use-Case is actually quite complex because many components are affected. Changing the volume might involve commanding a digital signal processor (DSP) and an amplifier in such a way that the quality of the audio signal is maintained while changing the volume. For example, rapid volume changes need to be damped because it would otherwise cause "clipping" which is disturbing to the user. This scenario is shown in detail in Figure 2.3. Note that three operations are identified, VolumeKeyPress, AdjustVolume and UpdateVolume. VolumeKeyPress takes care of the rotary button event handling. AdjustVolume interfaces with the DSP subsystem to actually change the volume and finally *UpdateVolume* which changes the volume setting on the display. Execution times and message sizes are estimated and annotated in the Sequence Diagram together with the two principle timing requirements applicable to this scenario. Priorities are defined in descending order (0 implies highest priority).

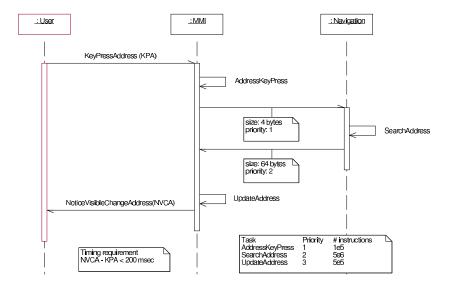

- 2. "Address Look-up" Destination entry is supported by a smart "typewriter" style interface. By turning a knob the user can move from letter to letter; by pressing it the user will select the currently highlighted letter. The map database is searched for each letter that is selected and only those letters in the on-screen alphabet are enabled that are potential next letters in the list. This scenario is shown in detail in Figure 2.4. Note that the SearchAddress operation is expensive compared to the other operations and that the size of the output value of the operation is 16 times larger than the input message.

- 3. "TMC Message Handling" Digital traffic information is important for in-car radio navigation systems. It enables features such as automatic re-planning of the

Figure 2.3: Annotated Sequence Diagram for "Change Volume"

Figure 2.4: Annotated Sequence Diagram for "Address Look-up"

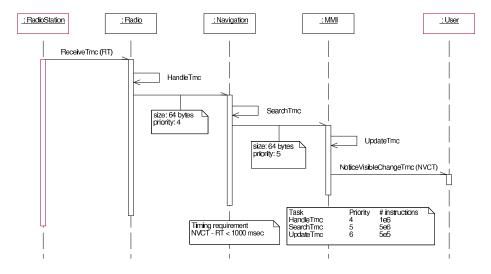

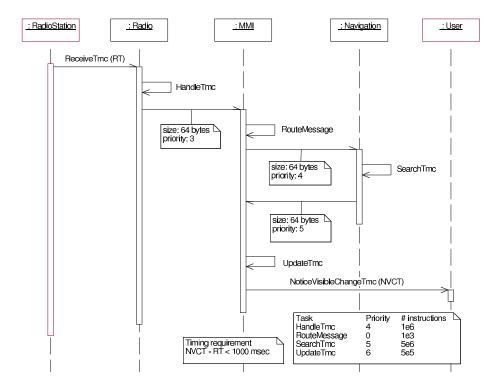

planned route in case a traffic jam occurs ahead. It is also increasingly important to enhance road safety by warning the driver, for example when a ghost driver is spotted just ahead on the planned route. TMC is such a digital traffic information service. TMC messages are broadcast by radio stations together with stereo audio sound. TMC messages are encoded: only problem location identifiers and message types are transmitted. The map database is accessed to translate these identifiers and to construct human readable text. The TMC message handling scenario is shown in Figure 2.5.

Figure 2.5: Annotated Sequence Diagram for "TMC Message Handling"

Note that the Sequence Diagrams are all annotated in such a way that they are useful for performance analysis. The order of magnitude of the numbers shown in the diagrams is realistic. This completes the first step of the recipe described in Section 2.1.

### Step 2 of the Y-chart approach - resource inventory

The scenarios have an interesting property: they can occur in parallel. TMC messages must be processed while the user changes the volume or enters a destination. However "Change Volume" and "Address Look-up" can not occur at the same time because they share a common resource; the rotary button is used for both. The architecture shown in Figure 2.2 suggests to assign the three clusters of functionality each to its own processing unit, whereby the computation resources are interconnected by a single communication bus.

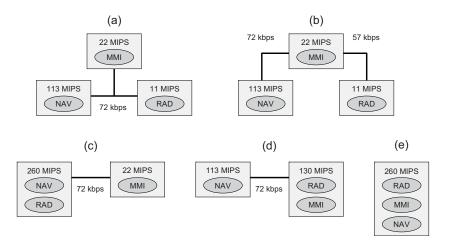

Figure 2.6 shows that there are more potential architectures that might be applicable. Note that the capacity of the resource units and communication infrastructure is quantified, completing step 2 of the recipe described in Section 2.1. The order of magnitude of the numbers shown in the diagram is correct; they are taken from the data sheets of several commercially available automotive CPUs. Observe that architecture (b) can only be evaluated if we introduce an additional operation on the MMI resource that transfers the data from one communication link to another, in the case that NAV wants to communicate to RAD or vice versa. This is the case for the "TMC Message Handling" scenario. The adapted Sequence Diagram for this special case is shown in Figure 2.7.

### 2.2.2 Modeling the environment

In order to analyze the proposed embedded architecture, we also need to characterize the so-called *workload* that the environment imposes onto the system. In this case study, we simply describe how often each application is invoked. We can abstract away from the complexity of the environment by describing the stimuli as a (p, j, d, o)-tuple.

Figure 2.6: Alternative system architectures to explore

Figure 2.7: Sequence Diagram for "TMC Message Handling" on architecture (b)

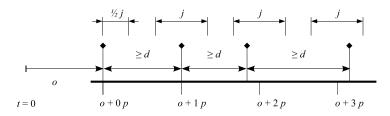

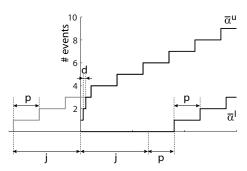

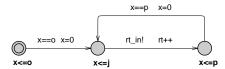

The p parameter describes the period of the stimulus, j describes the jitter, d the minimal inter arrival time and o the offset for the start of the first period. The most common stimuli arrival patterns can be described or approximated by this approach, including for example burst and sporadic behavior. The relationship between the parameters is graphically depicted in Figure 2.8. The (p, j, d, o)-tuple basically defines the *time in-*

*terval* in which a stimulus will occur. This model can be enriched with an additional stochastic variable which defines the distribution of the event within that interval. Similarly, the model can be extended to describe how much data is provided to the system at each event. But these extensions are out of scope for this thesis.

Figure 2.8: Workload definition using the (p, j, d, o)-notation

### 2.2.3 The modeling and analysis challenge

The generic question that is investigated in this chapter is how to distribute functionality over the available resources, such that all performance requirements are met. More specifically, some typical design-time questions can be formulated:

- **Design question 1**. Does the proposed architecture meet the performance requirements of all applications?

- **Design question 2**. How robust is the chosen architecture with respect to changes in application or architecture parameters?

- **Design question 3**. Is it possible to replace components by cheaper, less powerful, equivalents to save cost while maintaining the required performance targets?

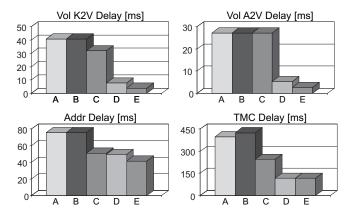

These questions will be addressed in sections 2.3.1 - 2.3.5 when the modeling techniques are introduced. The initial values for environment model used in this case study are shown in Table 2.1. The influence of the jitter, delay and offset parameters will be considered later. Fixed priority scheduling is assumed on all resources.

| Event name            | $\mathbf{period}\ p$ | jitter $j$ | $\mathbf{delay}\ d$ | offset o |

|-----------------------|----------------------|------------|---------------------|----------|

| KeyPressVolume (KPV)  | 31.25                | 0          | 0                   | 0        |

| KeyPressAddress (KPA) | 1000                 | 0          | 0                   | 0        |

| ReceiveTmc (RT)       | 3000                 | 0          | 0                   | 0        |

Table 2.1: Initial case study workload definitions (values in msec)

# 2.3 The performance modeling methods

The last step in the procedure proposed in Section 2.1 is to compose and analyze the abstract system performance model using some technique, based on the data collected in steps 1 and 2. We will demonstrate how this is done using Modular Performance Analysis (MPA) in Section 2.3.1, Symbolic Timing Analysis for Systems (SymTA/S) in Section 2.3.2, Timed Automata in Section 2.3.3, Parallel Object-Oriented Specification

Language (POOSL) in Section 2.3.4 and finally using the Vienna Development Method in Section 2.3.5. Each technique is introduced shortly and a flavor of the created system and environment models is given. The caveats of the modeling exercise are discussed and the analysis results obtained from these methods are compared in Section 2.4 in order to draw more general conclusions.

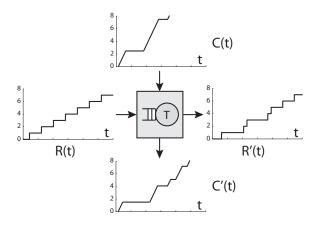

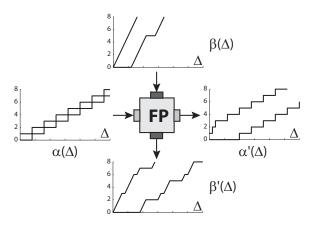

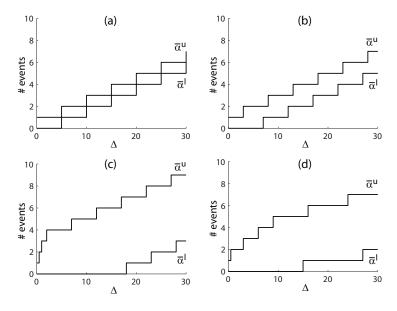

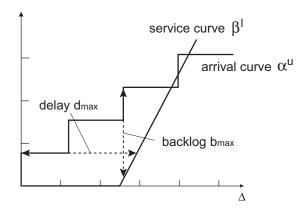

### 2.3.1 Modular Performance Analysis

### Short overview of the technique

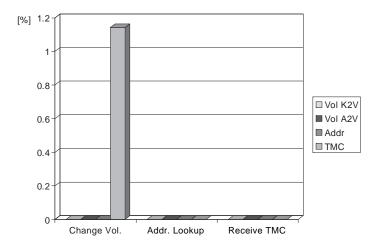

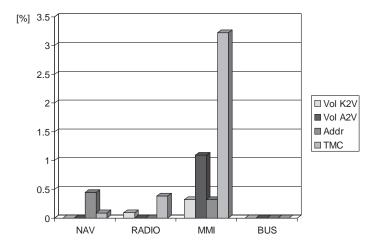

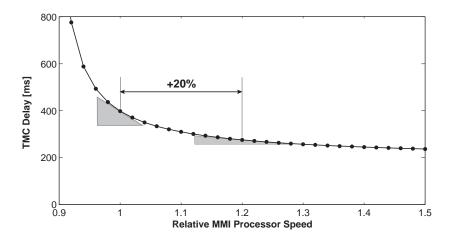

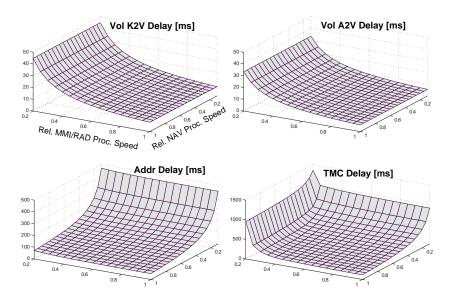

Modular Performance Analysis (MPA) was developed by Thiele et al at ETH Zürich [18]. MPA is a compositional modeling technique based on a general event and resource model. A set of basic building blocks, called *abstract components*, is available to build a queuing network that represents the system that we want to analyze. These abstract components are used to describe the handling of incoming events under the, possibly delayed, availability of resources. The events are described by a pair of interval bound functions  $\overline{\alpha}$ , the so-called lower and upper *arrival curves*  $\overline{\alpha}^l$  and  $\overline{\alpha}^u$ . These curves describe the respective bounds on the number of events that are to be handled by the component for any given interval size.  $\overline{\alpha}$  is also called the *event-based* arrival curve. Similarly, resources are described by a pair of interval bound functions  $\beta$ , the so-called lower and upper *service curves*  $\beta^l$  and  $\beta^u$ . These curves describe the bounds on the available resource capacity for any given interval size.